# Architecture & Pipelining (PIC 16F877A)

### What is PIC?

The term PIC or Peripheral Interface Controller, has been coined by Microchip Technology Inc.

Low-end range, mid-range and high end range of controllers.

#### **PIC Architecture: Background**

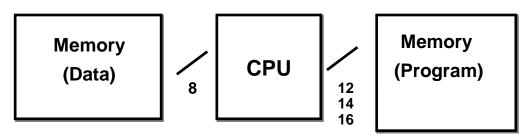

We're used to the <u>Von-Neuman Architecture</u>

- Used in: 80X86 (PCs), 8051, 68HC11, etc.)

- Only one bus between CPU and memory

- RAM and program memory share the same bus and the same memory, and so must have the same bit width

- Bottleneck: Getting instructions interferes with accessing RAM

### **PIC Architecture: Background**

#### PICs use the Harvard Architecture

- Used mostly in RISC CPUs (we'll get there)

- Separate program bus and data bus: can be different widths!

- For example, PICs use:

- Data memory (RAM): a small number of <u>8bit</u> registers

- Program memory (ROM): 12bit, 14bit or 16bit wide (in EPROM, FLASH, or ROM)

### CISC

Traditionally, CPUs are "CISC"

- Complex Instruction Set Computer (CISC)

- Used in: 80X86, 8051, 68HC11, etc.

- Many instructions (usually > 100)

- Many, many addressing modes

- Usually takes more than 1 internal clock cycle

(T cycle) to execute

- Example:

**MC68HC05**:

| 1000 | 1100 |

|------|------|

| 0101 | 0101 |

## RISC

PICs and most Harvard chips are "RISC"

- Reduced Instruction Set Computer (RISC)

- Used in: SPARC, ALPHA, Atmel AVR, etc.

- ✤ Few instructions (usually < 50)</p>

- Only a few addressing modes

- Executes 1 instruction in 1 internal clock cycle (Tcyc)

- Example:

PIC16CXXX:

1100XX 01010101

## What is New in PIC?

- High performance RISC CPU with 35 no. of instruction set only

- Harvard Architecture

- Pipelined Instructions

- And a large number of Peripherals In-built

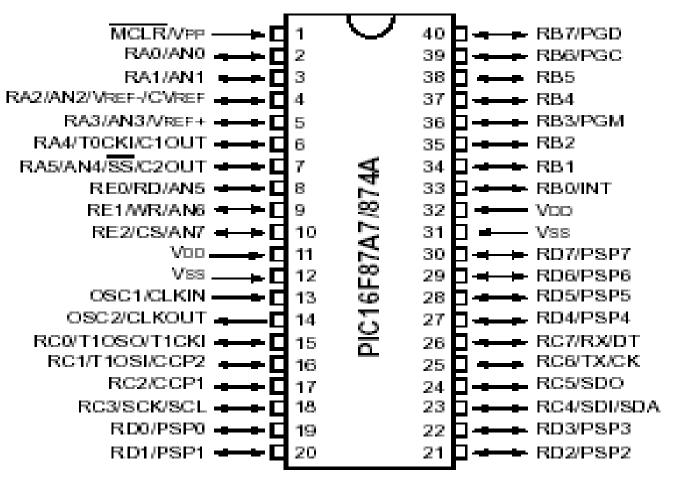

## **Pin Diagram**

#### PDIP (40 pin)

### Features

- 8kB of flash program memory

- 368bytes of Data memory

- 256-EEPROM data memory

- 15 Interrupts

- In-circuit programming

- 3 internal hardware timers

- Capture/Compare/PW

M modules

- Up to 8 channels of 10-Bit A/D

- Built-in USART for serial communication

- 5 digital I/O ports (Up to 22 lines)

#### **I/O Ports**

- PIC 16F877A has FIVE I/O Ports

- A total of 33 pins are used for I/O operations.

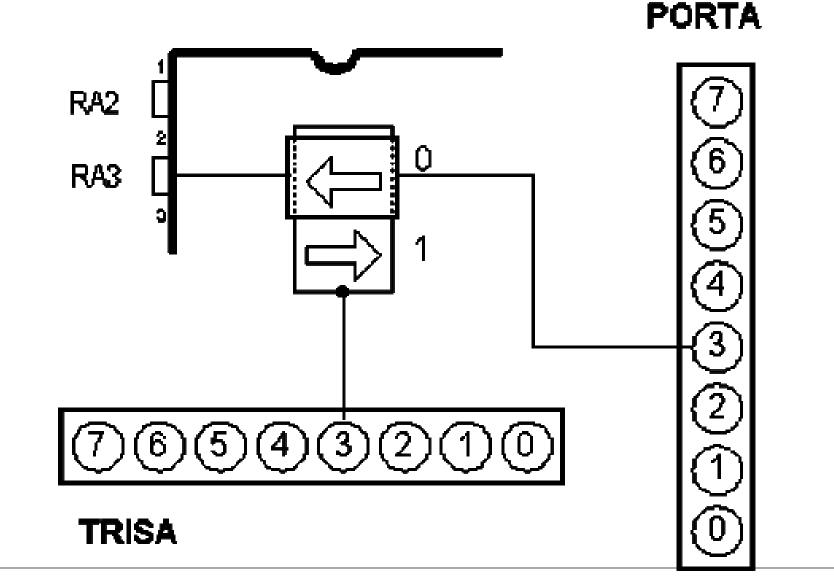

#### PORT A

- Port A is 6 bit wide and bi-directional.

- Its corresponding data direction register is TRISA.

- If TRISA port pin is set to 1, corresponding port A pin will act as an input pin and vice versa.

- Port A is used for analog inputs.

#### **Port B**

- Port B is 8 bit wide and bi-directional.

- Its corresponding data direction register is TRISB.

- If TRISB port pin is set to 1, corresponding port B pin will act as an input pin and vice versa.

- Port B is used for Data Transmission.

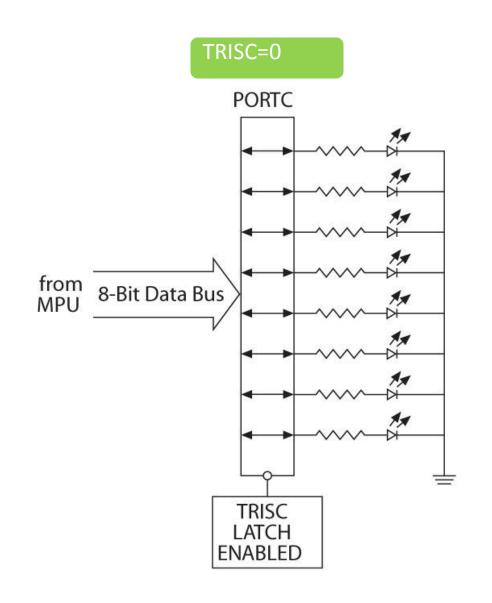

## **Port C**

- Port C is 8 bit wide and bi-directional.

- Its corresponding data direction register is TRISC.

- If TRISC port pin is set to 1, corresponding port C pin will act as an input pin and vice versa.

- Port C is used for control registers(serial communication, I2C functions, serial data transfer).

## Port D

- Port D is 8 bit wide and bi-directional.

- Its corresponding data direction register is TRISD.

- If TRISD port pin is set to 1, corresponding port D pin will act as an input pin and vice versa.

- Port D is used as Data port

### **Port E**

- Port E is 3 bit wide . They are for read, write and chip select operation.

- Each pin is individually configurable as inputs and outputs.

- Port E is generally used for controlling purposes.

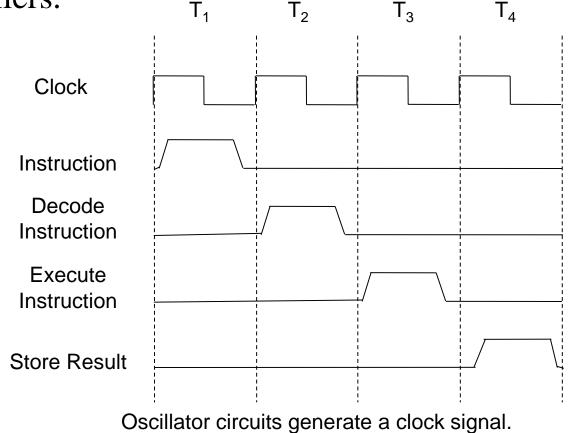

#### **Machine Cycle**

4 cycles per4 cycles per instruction on the PIC16F87x micro controllers. instruction on the PIC16F87x micro controllers.

### Calculations

- A Machine cycle is the time taken for a data transfer from or to memory/ I/O Ports.

- Machine cycle is calculated using the formula: Clock Frequency=6.144MHz

Machine cycle frequency= 6.144 MHz /4

Hence 1 Machine cycle(Time taken for a data transfer)= 1/T

= 4/ 6.144 MHz

$= 0.651 \ \mu s$

## **Instruction Cycle**

- An instruction cycle is the time taken to complete an instruction.

- All instructions in 16F877A are single cycle instructions except for Branching instruction. They take two machine cycles to complete an instruction.

## **PIC overview**

Different PICs have different on-board peripherals some common peripherals are:

- \* 3 Timers (0 & 2- 8bits, 1-16 bits)

- 2 Compare/Capture/PWM Modules

- Analog to Digital Converters (ADC) (8, 10 and 12bit, 50ksps)

- Serial communications: UART (RS-232C), SPI, I<sup>2</sup>C, CAN

- Pulse Width Modulation (PWM) (10bit)

- Voltage Comparators

- Voltage Reference Modules

- MSSP Master Synchronous Serial Port

- I2C (Master and Slave)

- SPI (Master and Slave)

- Watchdog timers, Brown out detect, LCD drivers

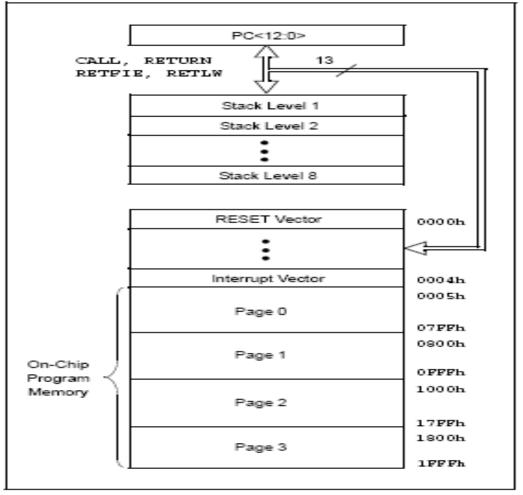

#### Instructions

Memory Organisation

#### FIGURE 2-1: PIC16F876A/877A PROGRAM MEMORY MAP AND STACK

## **Data Memory Organisation**

- The data memory partitioned into General Purpose registers and Special Function Registers.

- Bits RP1 and RP0 are the bank select bits.

| RP1 | RP0 | Bank |

|-----|-----|------|

| 0   | 0   | 0    |

| 0   | 1   | 1    |

| 1   | 0   | 2    |

| 1   | 1   | 3    |

|                                         | A                   | File<br>\ddress | . ,                  | File<br>Address |                     | File<br>Address |                         | File<br>Address |

|-----------------------------------------|---------------------|-----------------|----------------------|-----------------|---------------------|-----------------|-------------------------|-----------------|

| Indirect ad                             | ddr. <sup>(*)</sup> | 00h             | Indirect addr.(*)    | 80h             | Indirect addr.(*)   | 100h            | Indirect addr.(*)       | 180h            |

| TMR                                     |                     | 01h             | OPTION_REG           | 81h             | TMR0                | 101h            | OPTION_REG              | 181h            |

| PCL                                     | -                   | 02h             | PCL                  | 82h             | PCL                 | 102h            | PCL                     | 182h            |

| STATU                                   | IS                  | 03h             | STATUS               | 83h             | STATUS              | 103h            | STATUS                  | 183h            |

| FSR                                     |                     | 04h             | FSR                  | 84h             | FSR                 | 104h            | FSR                     | 184h            |

| PORT                                    |                     | 05h             | TRISA                | 85h             |                     | 105h            |                         | 185h            |

| PORT                                    | в                   | 06h             | TRISB                | 86h             | PORTB               | 106h            | TRISB                   | 186h            |

| PORT                                    | C                   | 07h             | TRISC                | 87h             |                     | 107h            |                         | 187h            |

| PORTE                                   | D <sup>(1)</sup>    | 08h             | TRISD <sup>(1)</sup> | 88h             |                     | 108h            |                         | 188h            |

| PORTE                                   | (1)                 | 09h             | TRISE <sup>(1)</sup> | 89h             |                     | 109h            |                         | 189h            |

| PCLAT                                   | ΓH                  | 0Ah             | PCLATH               | 8Ah             | PCLATH              | 10Ah            | PCLATH                  | 18Ah            |

| INTCC                                   | DN                  | 0Bh             | INTCON               | 8Bh             | INTCON              | 10Bh            | INTCON                  | 18Bh            |

| PIR1                                    |                     | 0Ch             | PIE1                 | 8Ch             | EEDATA              | 10Ch            | EECON1                  | 18Ch            |

| PIR2                                    | 2                   | 0Dh             | PIE2                 | 8Dh             | EEADR               | 10Dh            | EECON2                  | 18Dh            |

| TMR1                                    | IL                  | 0Eh             | PCON                 | 8Eh             | EEDATH              | 10Eh            | Reserved <sup>(2)</sup> | 18Eh            |

| TMR1                                    | Н                   | 0Fh             |                      | 8Fh             | EEADRH              | 10Fh            | Reserved <sup>(2)</sup> | 18Fh            |

| T1CO                                    |                     | 10h             |                      | 90h             |                     | 110h            |                         | 190h            |

| TMR                                     |                     | 11h             | SSPCON2              | 91h             |                     | 111h            |                         | 191h            |

| T2CO                                    |                     | 12h             | PR2                  | 92h             |                     | 112h            |                         | 192h            |

| SSPBL                                   |                     | 13h             | SSPADD               | 93h             |                     | 113h            |                         | 193h            |

| SSPCC                                   |                     | 14h             | SSPSTAT              | 94h             |                     | 114h            |                         | 194h            |

| CCPR                                    |                     | 15h             |                      | 95h             |                     | 115h            |                         | 195h            |

| CCPR'                                   |                     | 16h             |                      | 96h             | General             | 116h            | General                 | 196h            |

| CCP1C                                   |                     | 17h             |                      | 97h             | Purpose             | 117h            | Purpose                 | 197h            |

| RCST                                    |                     | 18h             | TXSTA                | 98h             | Register            | 118h            | Register                | 198h            |

| TXRE                                    |                     | 19h             | SPBRG                | 99h             | 16 Bytes            | 119h            | 16 Bytes                | 199h            |

| RCRE                                    |                     | 1Ah             |                      | 9Ah             |                     | 11Ah<br>11Bh    |                         | 19Ah            |

| CCPR                                    |                     | 1Bh             | CMCON                | 9Bh             |                     | 11Bh<br>11Ch    |                         | 19Bh            |

| CCPR<br>CCP2C                           |                     | 1Ch<br>1Dh      | CMCON<br>CVRCON      | 9Ch<br>9Dh      |                     | 11Ch<br>11Dh    |                         | 19Ch<br>19Dh    |

| ADRES                                   |                     | 1Eh             | ADRESL               | 9Eh             |                     | 11Eh            |                         | 19Eh            |

| ADCO                                    |                     | 1Fh             | ADCON1               | 9Fh             |                     | 11Fh            |                         | 19Fh            |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                     | 20h             |                      | A0h             |                     | 120h            |                         | 1A0h            |

|                                         |                     |                 |                      | AUT             |                     |                 |                         | IAUG            |

| Genera                                  |                     |                 | General              |                 | General             |                 | General                 |                 |

| Purpos<br>Registe                       |                     |                 | Purpose<br>Register  |                 | Purpose<br>Register |                 | Purpose<br>Register     |                 |

| -                                       |                     |                 | 80 Bytes             |                 | 80 Bytes            |                 | 80 Bytes                | 4556            |

| 96 Byte                                 | es                  |                 | ,                    | EFh             | ,                   | 16Fh            |                         | 1EFh<br>1F0h    |

|                                         |                     |                 | accesses             | F0h             | accesses            | 170h            | accesses<br>70h - 7Fh   | TFUN            |

|                                         |                     | 7Fh             | 70h-7Fh              | FFh             | 70h-7Fh             | 17Fh            | /UN-/FN                 | 1FFh            |

| Bank 0                                  | )                   |                 | Bank 1               |                 | Bank 2              |                 | Bank 3                  |                 |

#### Timers

PIC16F877A has 3 Timers

Timer 0 - 8 bit

can be used as a Timer/counter

⋆ Timer 1 – 16 bit

can be used as a Timer/counter

• Timer 2 - 8 bit Timer

can be used as the PWM time-base for the PWM mode of the CCP module.

#### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

|         | U-0                                                                                                                                                | U-0                           | R/W-0                          | R/W-0          | R/W-0             | R/W-0    | R/W-0  | R/W-0  |  |  |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------|----------------|-------------------|----------|--------|--------|--|--|--|--|--|--|

|         | _                                                                                                                                                  | _                             | T1CKPS1                        | T1CKPS0        | T1OSCEN           | T1SYNC   | TMR1CS | TMR10N |  |  |  |  |  |  |

|         | bit 7                                                                                                                                              |                               |                                |                |                   |          |        | bit 0  |  |  |  |  |  |  |

|         |                                                                                                                                                    |                               |                                |                |                   |          |        |        |  |  |  |  |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                         |                               |                                |                |                   |          |        |        |  |  |  |  |  |  |

| bit 5-4 | T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits                                                                                           |                               |                                |                |                   |          |        |        |  |  |  |  |  |  |

|         | 11 = 1:8 Prescale value<br>10 = 1:4 Prescale value<br>01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                           |                               |                                |                |                   |          |        |        |  |  |  |  |  |  |

| bit 3   | T10SCEN: Timer1 Oscillator Enable Control bit                                                                                                      |                               |                                |                |                   |          |        |        |  |  |  |  |  |  |

|         | <ul> <li>1 = Oscillator is enabled</li> <li>0 = Oscillator is shut-off (the oscillator inverter is turned off to eliminate power drain)</li> </ul> |                               |                                |                |                   |          |        |        |  |  |  |  |  |  |

| bit 2   | T1SYNC:                                                                                                                                            | Timer1 Exte                   | ernal Clock li                 | nput Synchr    | onization Contr   | ol bit   |        |        |  |  |  |  |  |  |

|         | When TMF                                                                                                                                           |                               |                                |                |                   |          |        |        |  |  |  |  |  |  |

|         |                                                                                                                                                    | -                             | e external cl<br>nal clock ing |                |                   |          |        |        |  |  |  |  |  |  |

|         | When TMF                                                                                                                                           |                               | nar ciocit ing                 | , at           |                   |          |        |        |  |  |  |  |  |  |

|         | This bit is i                                                                                                                                      | gnored. Tin                   | ner1 uses th                   | e internal clo | ock when TMR      | 1CS = 0. |        |        |  |  |  |  |  |  |

| bit 1   | TMR1CS:                                                                                                                                            | Timer1 Clo                    | ck Source S                    | elect bit      |                   |          |        |        |  |  |  |  |  |  |

|         |                                                                                                                                                    | al clock from<br>I clock (Fos |                                | 10S0/T1CF      | (I (on the rising | edge)    |        |        |  |  |  |  |  |  |

| bit 0   | TMR10N:                                                                                                                                            | Timer1 On                     | bit                            |                |                   |          |        |        |  |  |  |  |  |  |

|         | 1 = Enable                                                                                                                                         |                               |                                |                |                   |          |        |        |  |  |  |  |  |  |

|         | o = Stops                                                                                                                                          | l imer1                       |                                |                |                   |          |        |        |  |  |  |  |  |  |

|         | Lanard                                                                                                                                             |                               |                                |                |                   |          |        |        |  |  |  |  |  |  |

|         | Legend:                                                                                                                                            |                               |                                |                |                   |          |        |        |  |  |  |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented I  | oit, read as 'O'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## Timer 1

- \* The data registers of Timer 1 are TMR1H and TMR1L.

- The 16 bit value to be loaded in the timer is given to Data registers

- \* The Control register is T1CON.

- The timer ON and oscillator enable operations are controlled through the control register.

- To determine if the timer has completed its operation, the timer overflow bit TMR1IF of the PIR1 register is checked continuously.

## **USART**

- Universal synchronous asynchronous receiver transmitter is also known as a serial communication interface.

- USART can be configured in the following modes:

- Asynchronous FULL DUPLEX

- synchronous HALF DUPLEX

### **Serial Communication**

- For serial Communication, the SFR involved are TXSTA, TXREG, RCSTA,,RCREG and SPBRG.

- SPBRG is used to set the required baud rate.

- In TXSTA,TXEN is set high to enable transmission.

- The transmitted data is stored in a temporary buffer,TXREG.

- In RCSTA, SPEN and CREN are set high to enable reception.

- The received data is stored in a temporary buffer, RCREG.

#### REGISTER 10-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

|       | R/W-0                        | R/W-0        | R/W-0         | R/W-0         | U-0    | R/W-0 | R-1  | R/W-0 |

|-------|------------------------------|--------------|---------------|---------------|--------|-------|------|-------|

|       | CSRC                         | TX9          | TXEN          | SYNC          | -      | BRGH  | TRMT | TX9D  |

|       | bit 7                        |              |               |               |        |       |      | bit 0 |

|       |                              |              |               |               |        |       |      |       |

| bit 7 | CSRC: Cloc                   | k Source Se  | elect bit     |               |        |       |      |       |

|       | Asynchronou<br>Don't care    | us mode:     |               |               |        |       |      |       |

|       | Synchronous                  |              |               |               |        |       |      |       |

|       | 1 = Master n<br>0 = Slave ma |              |               |               | m BRG) |       |      |       |

| bit 6 | TX9: 9-bit Tr                |              |               | ,             |        |       |      |       |

|       | 1 = Selects §                |              |               |               |        |       |      |       |

|       | 0 = Selects 8                |              |               |               |        |       |      |       |

| bit 5 | TXEN: Tran<br>1 = Transmit   |              | bit           |               |        |       |      |       |

|       | 0 = Transmit                 |              |               |               |        |       |      |       |

|       | Note: SREN                   | //CREN ove   | rrides TXEN   | in SYNC m     | iode.  |       |      |       |

| bit 4 | SYNC: USA                    |              | elect bit     |               |        |       |      |       |

|       | 1 = Synchro                  |              |               |               |        |       |      |       |

| bit 3 | 0 = Asynchro                 |              |               |               |        |       |      |       |

| bit 2 | Unimplement<br>BBCU: Uich    |              |               |               |        |       |      |       |

| DIL 2 | BRGH: High<br>Asynchronou    |              | Select bit    |               |        |       |      |       |

|       | 1 = High spe                 |              |               |               |        |       |      |       |

|       | 0 = Low spe                  | ed           |               |               |        |       |      |       |

|       | Synchronous<br>Unused in th  |              |               |               |        |       |      |       |

| bit 1 | TRMT: Trans                  |              | gister Statu  | s bit         |        |       |      |       |

|       | 1 = TSR emp<br>0 = TSR full  | pty          |               |               |        |       |      |       |

| bit O | TX9D: 9th bi                 | t of Transmi | Data ora      | ha Parity bi  |        |       |      |       |

| UIL U | ASD. SHID                    | tor nansmi   | it Data, carr | be Faility bi |        |       |      |       |

#### REGISTER 10-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R-0  | R-0  | R-x   | _ |

|-------|-------|-------|-------|-------|------|------|-------|---|

| SPEN  | RX9   | SREN  | CREN  | ADDEN | FERR | OERR | RX9D  |   |

| bit 7 |       |       |       |       |      |      | bit 0 |   |

| bit 7 | SPEN: Serial Port Enable bit<br>1 = Serial port enabled (configures RC7/RX/DT and RC8/TX/CK pins as serial port pins)<br>0 = Serial port disabled                                                                                                                                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | RX9: 9-bit Receive Enable bit<br>1 = Selects 9-bit reception<br>0 = Selects 8-bit reception                                                                                                                                                                                                                                                                                 |

| bit 5 | SREN: Single Receive Enable bit<br><u>Asynchronous mode:</u><br>Don't care<br><u>Synchronous mode - Master:</u><br>1 = Enables single receive<br>0 = Disables single receive<br>This bit is cleared after reception is complete.<br>Symphones mode - Slave:                                                                                                                 |

|       | Synchronous mode - Slave:<br>Don't care                                                                                                                                                                                                                                                                                                                                     |

| bit 4 | CREN: Continuous Receive Enable bit<br><u>Asynchronous mode:</u><br>1 = Enables continuous receive<br>0 = Disables continuous receive<br><u>Synchronous mode:</u><br>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)                                                                                                                  |

| bit 3 | <ul> <li>0 = Disables continuous receive</li> <li>ADDEN: Address Detect Enable bit</li> <li><u>Asynchronous mode 9-bit (RX9 = 1):</u></li> <li>1 = Enables address detection, enables interrupt and load of the receive buffer when RSR&lt;8&gt; is set</li> <li>a = Disables address detection, ell butto are provided and picth bit are be used as active bit.</li> </ul> |

| bit 2 | 0 = Disables address detection, all bytes are received, and ninth bit can be used as parity bit<br>FERR: Framing Error bit<br>1 = Framing error (can be updated by reading RCREG register and receive next valid byte)<br>0 = No framing error                                                                                                                              |

| bit 1 | OERR: Overrun Error bit<br>1 = Overrun error (can be cleared by clearing bit CREN)<br>0 = No overrun error                                                                                                                                                                                                                                                                  |

| bit O | RX9D: 9th bit of Received Data (can be parity bit, but must be calculated by user firmware)                                                                                                                                                                                                                                                                                 |

|       | I                                                                                                                                                                                                                                                                                                                                                                           |

| Legend:                     |                  |                                         |

|-----------------------------|------------------|-----------------------------------------|

| Legend:<br>R = Readable bit | W = Writable bit | U = Unimplemented bit, read as '0'      |

| - n = Value at POR          | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

#### TABLE 10-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7   | Bit 6     | Bit 5    | Bi    | t 4    | Bit        | 3         | Bit 2 | 2    | Bit 1 | Bit  |      | Value on<br>POR,<br>BOR | a         | alue on<br>II other<br>ESETS |

|---------|-------|---------|-----------|----------|-------|--------|------------|-----------|-------|------|-------|------|------|-------------------------|-----------|------------------------------|

| 98h     | TXSTA | CSRC    | TX9       | TXEN     | SY    | NC     | _          |           | BRG   | н    | TRMT  | TX9  | D    | 0000 -03                | LO 00     | 00 -010                      |

| 18h     | RCSTA | SPEN    | RX9       | SREN     | CR    | EN     | ADD        | EN        | FER   | R    | OERR  | RX9  | D    | 000 000                 | 00 x      | x000 00                      |

| 99h     | SPBRG | Baud Ra | te Genera | ator Reg | ister |        |            |           |       |      |       |      | (    | 000 000                 |           | 00 0000                      |

|         |       |         |           | 98h      | TXSTA | CSRC   | TX9        | TXEN      | SYNC  |      | BRGH  | TRMT | TX9D | 0000 -010               | 0000 -010 | =                            |

|         |       |         |           |          | RCSTA | SPEN   |            | SREN      | CREN  | ADDE |       | OERR |      |                         | 0000 0002 | -                            |

|         |       |         |           | 99h      | SPBRG | Baud R | ate Genera | ator Regi | ster  |      |       |      |      | 0000 0000               | 0000 0000 | 7                            |

99h

SPBRG

Baud Rate Generator Register

Legend:

x

- unknown, - - unimplemented, read as '0'. Shaded cells are not used by the BRG.

#### FOR BAUD RATE:

For asynchronous mode, Baud rate=Fosc / 64(x+1)For synchronous mode, Baud rate=Fosc / 4(x+1)

#### FOR RECEPTION:

Check RCIF flag till it is set. This indicates that the data is completely received in the RCREG. Move this value to working register for further manipulation.

#### FOR TRANSMISSION:

To transmit the calculated data, move the value to TXREG. Check the TXIF flag till it is set. This indicates that the data is completely transmitted out.

#### REGISTER 2-5: PIR1 REGISTER (ADDRESS 0Ch)

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |  |

|----------------------|-------|------|------|-------|--------|--------|--------|--|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |  |

| bit 7                |       |      |      |       |        |        | bit O  |  |

PSPIF: Parallel Slave Port Read/Write Interrupt Flag bit<sup>(1)</sup> bit 7

A read or a write operation has taken place (must be cleared in software)

o = No read or write has occurred

Note 1: PSPIF is reserved on PIC16F873A/876A devices; always maintain this bit clear.

- bit 6 ADIF: A/D Converter Interrupt Flag bit

- An A/D conversion completed

- o = The A/D conversion is not complete

- bit 5 RCIF: USART Receive Interrupt Flag bit

- The USART receive buffer is full

- o = The USART receive buffer is empty

- blt 4 TXIF: USART Transmit Interrupt Flag bit

- The USART transmit buffer is empty

- o = The USART transmit buffer is full

- blt 3 SSPIF: Synchronous Serial Port (SSP) Interrupt Flag bit

- 1 The SSP interrupt condition has occurred, and must be cleared in software before returning. from the Interrupt Service Routine. The conditions that will set this bit are:

- SPI

- A transmission/reception has taken place.

- I<sup>2</sup>C Slave

- A transmission/reception has taken place.

- I<sup>2</sup>C Master

- A transmission/reception has taken place.

- The initiated START condition was completed by the SSP module.

- The initiated STOP condition was completed by the SSP module.

- The initiated Restart condition was completed by the SSP module.

- The initiated Acknowledge condition was completed by the SSP module.

- A START condition occurred while the SSP module was idle (Multi-Master system).

- A STOP condition occurred while the SSP module was idle (Multi-Master system).

- o = No SSP Interrupt condition has occurred.

- blt 2 CCP1IF: CCP1 Interrupt Flag bit

Capture mode:

- 1 = A TMR1 register capture occurred (must be cleared in software)

- o = No TMR1 register capture occurred

Compare mode:

- A TMR1 register compare match occurred (must be cleared in software)

- o = No TMR1 register compare match occurred

PWM mode:

Unused in this mode

R = Readable bit

- TMR2IF: TMR2 to PR2 Match Interrupt Flag bit bit 1

- TMR2 to PR2 match occurred (must be cleared in software)

- o = No TMR2 to PR2 match occurred

#### bit 0 TMR1IF: TMR1 Overflow Interrupt Flag bit

1 = TMR1 register overflowed (must be cleared in software)

W - Writable bit

o = TMR1 register did not overflow

Legend:

- U Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set

- '0' = Bit is cleared

- x = Bit is unknown

## Interrupts

- PIC16F877A has 15 sources of interrupts.

- Only one vector location is allocated for the interrupts.

- The Global interrupt enable bit is set, so that any interrupt can be acknowledged.

- Regardless of the Global enable bit, the user should ensure, the appropriate interrupt flag bits that needs to be executed, is also set.

#### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

|       | R/W-0                                                                                                                                                                                                                     | R/W-0                     | R/W-0                      | R/W-0       | R/W-0        | R/W-0        | R/W-0       | R/W-x |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------|-------------|--------------|--------------|-------------|-------|

|       | GIE                                                                                                                                                                                                                       | PEIE                      | TMROIE                     | INTE        | RBIE         | TMROIF       | INTF        | RBIF  |

|       | bit 7                                                                                                                                                                                                                     |                           |                            |             |              |              |             | bit 0 |

| bit 7 | GIE: Globa                                                                                                                                                                                                                | al Interrupt E            | nable bit                  |             |              |              |             |       |

|       | 1 = Enables all unmasked interrupts<br>0 = Disables all interrupts                                                                                                                                                        |                           |                            |             |              |              |             |       |

| bit 6 | PEIE: Perij                                                                                                                                                                                                               | pheral Interr             | upt Enable b               | it          |              |              |             |       |

|       | 1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                                                                                                  |                           |                            |             |              |              |             |       |

| oit 5 | TMR0IE: T                                                                                                                                                                                                                 | MR0 Overfi                | ow Interrupt               | Enable bit  |              |              |             |       |

|       |                                                                                                                                                                                                                           | s the TMR0<br>as the TMR0 |                            |             |              |              |             |       |

| oit 4 | INTE: RB0                                                                                                                                                                                                                 | /INT Externa              | al Interrupt E             | nable bit   |              |              |             |       |

|       | 1 = Enables the RB0/INT external interrupt<br>0 = Disables the RB0/INT external interrupt                                                                                                                                 |                           |                            |             |              |              |             |       |

| vit 3 | RBIE: RB I                                                                                                                                                                                                                | Port Change               | e Interrupt Er             | nable bit   |              |              |             |       |

|       | 1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt                                                                                                                                     |                           |                            |             |              |              |             |       |

| it 2  | TMR0IF: T                                                                                                                                                                                                                 | MR0 Overfic               | ow Interrupt               | Flag bit    |              |              |             |       |

|       |                                                                                                                                                                                                                           | ~                         | overflowed<br>not overflow | 3           | ared in soft | ware)        |             |       |

| xit 1 | INTF: RB0                                                                                                                                                                                                                 | /INT Externa              | al Interrupt F             | lag bit     |              |              |             |       |

|       | 1 = The RB0/INT external interrupt occurred (must be cleared in software)<br>0 = The RB0/INT external interrupt did not occur                                                                                             |                           |                            |             |              |              |             |       |

| vit O | RBIF: RB F                                                                                                                                                                                                                | Port Change               | Interrupt Fla              | ag bit      |              |              |             |       |

|       | 1 = At least one of the RB7:RB4 pins changed state; a mismatch condition will continue to set<br>the bit. Reading PORTB will end the mismatch condition and allow the bit to be cleared<br>(must be cleared in software). |                           |                            |             |              |              |             |       |

|       |                                                                                                                                                                                                                           |                           | B4 pins hav                | e changed s | state        |              |             |       |

|       | Legend:                                                                                                                                                                                                                   |                           |                            |             |              |              |             |       |

|       | R = Reada                                                                                                                                                                                                                 | hle hit                   | W = W                      | ritable hit | U = Unin     | nlamantari l | hit read as | ·0·   |

| Legend:            |                  |                                         |

|--------------------|------------------|-----------------------------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'      |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

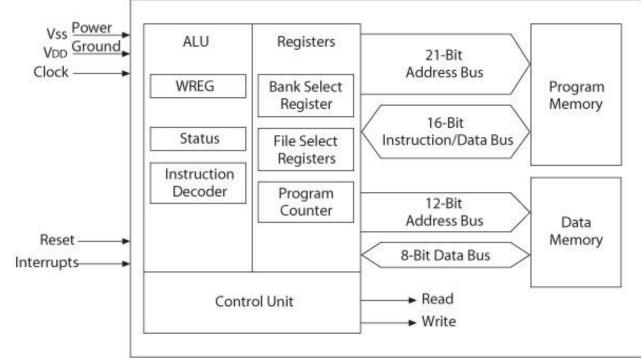

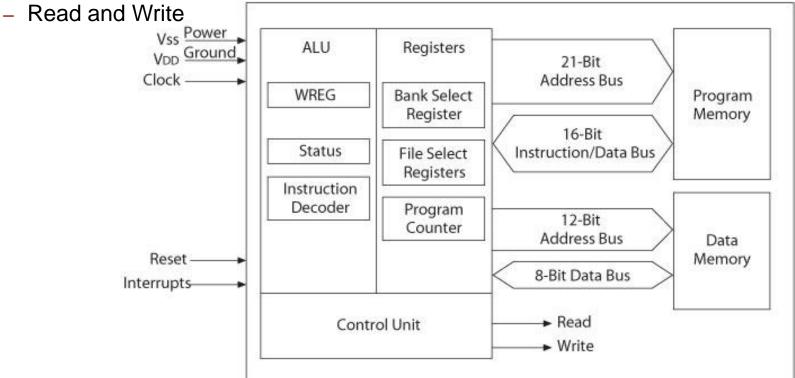

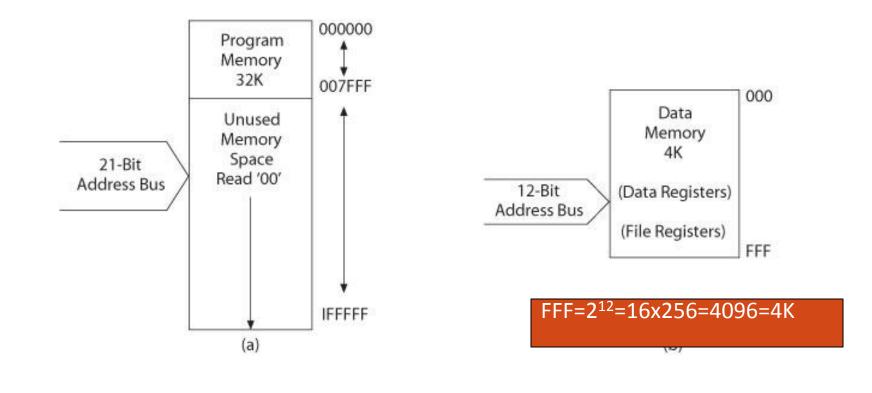

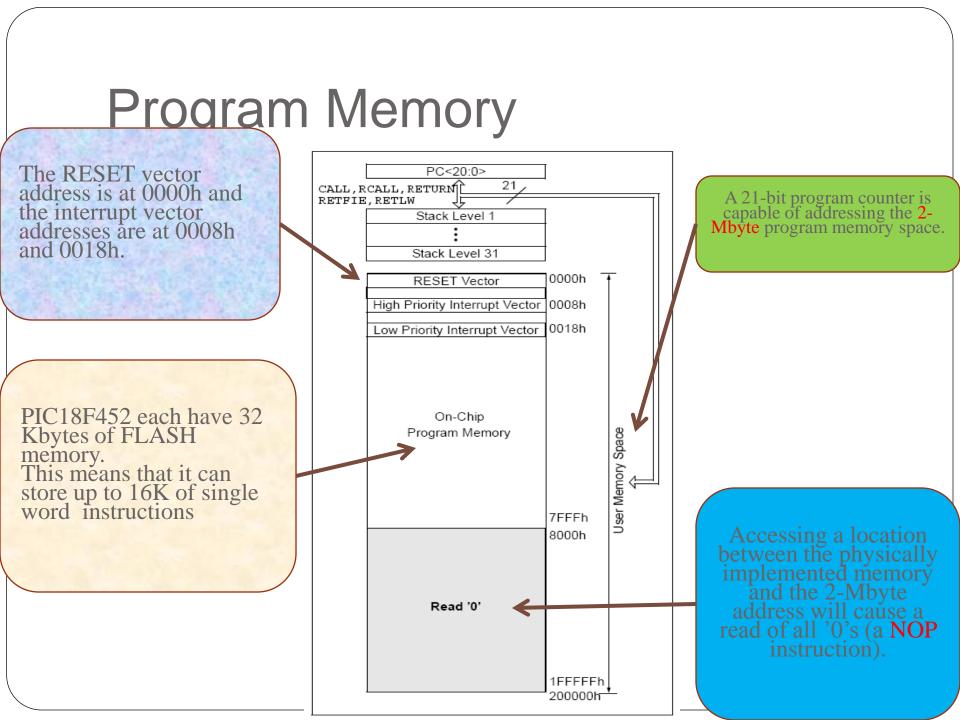

## PIC18F - Address Buses

- Address bus

- 21-bit address bus for program memory addressing capacity: 2 MB of memory

- 12-bit address bus for data memory addressing capacity: 4 KB of memory

## Data Bus and Control Signals

#### Data bus

- 16-bit instruction/data bus for program memory

- 8-bit data bus for data memory

#### Control signals

#### PIC18F452/4520 Memory

- Program memory with addresses (Flash)

- Data memory with addresses

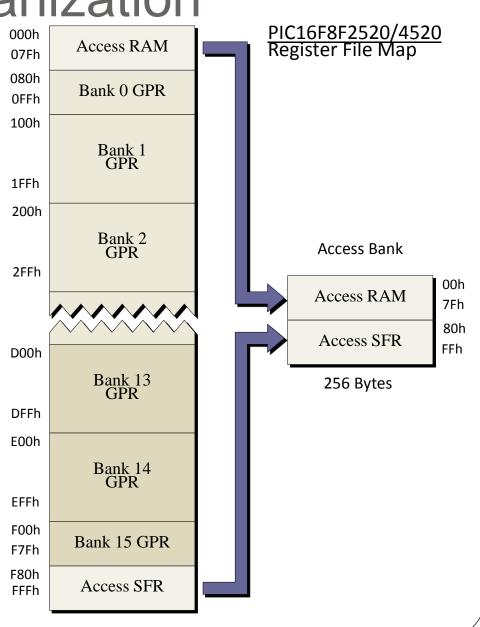

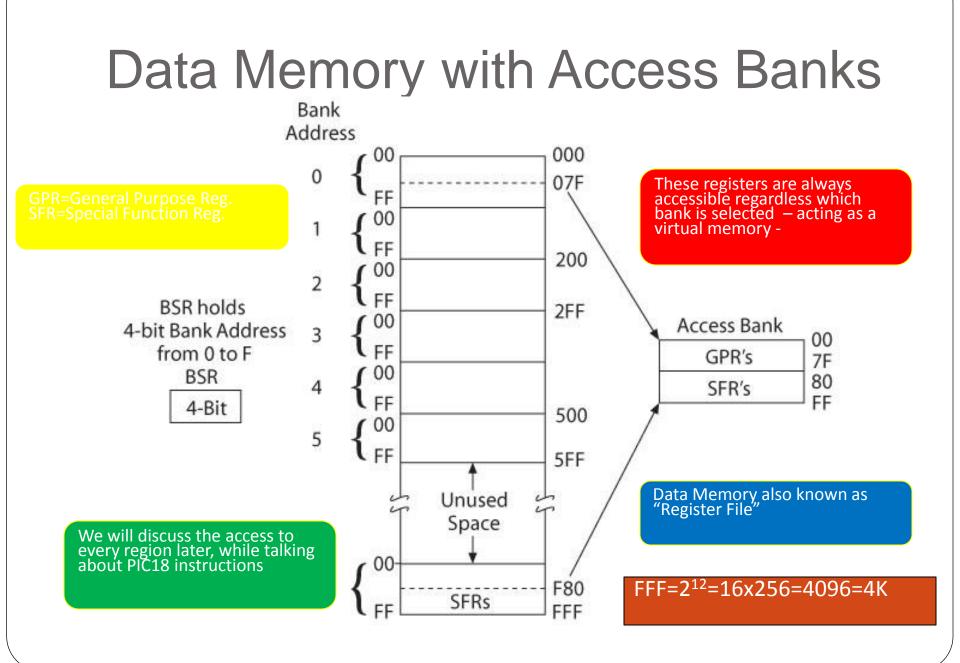

## Data Memory Organization

- Data Memory up to 4k bytes

- Divided into 256 byte banks

- Half of bank 0 and half of bank 15 form a virtual bank that is accessible no matter which bank is selected

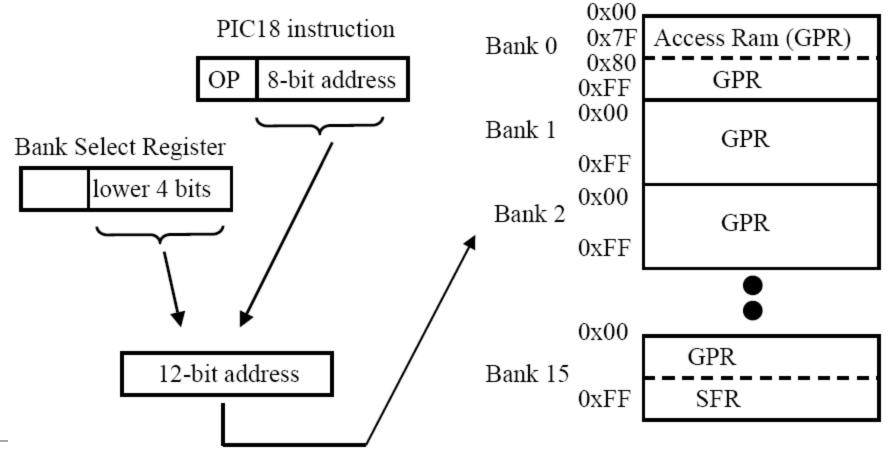

## Accessing Data Memory

The machine code for a PIC18 instruction has only 8 bits for a data memory address which needs 12 bits. The Bank Select Register (BSR) supplies the other 4

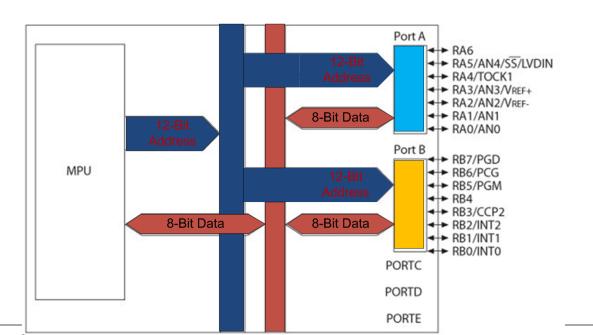

#### PIC18F452 I/O Ports

- Five I/O ports

- PORT A through PORT E

- Most I/O pins are multiplexed

- Generally have eight I/O pins with a few exceptions

- Addresses already assigned to these ports in the design stage

- Each port is identified by its assigned SFR

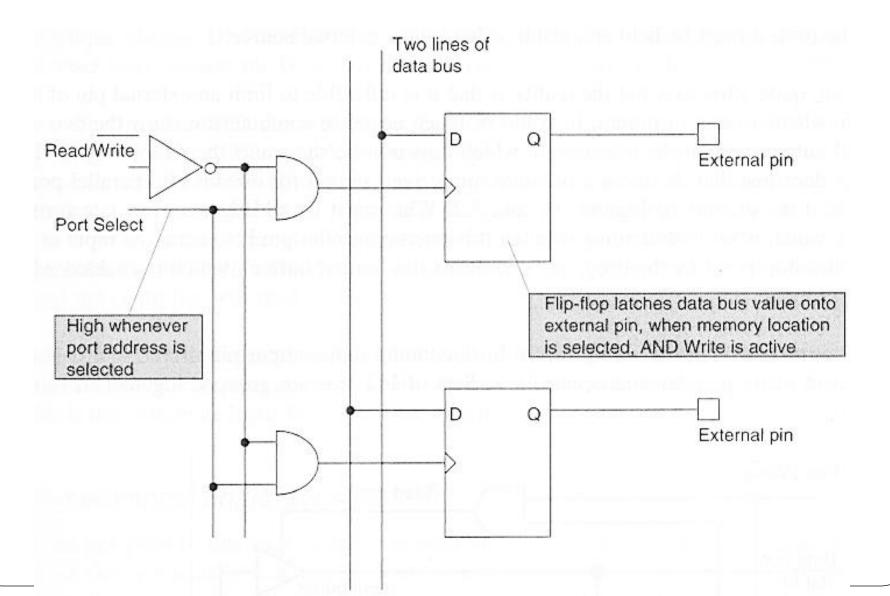

#### Parallel I/O Output Structure

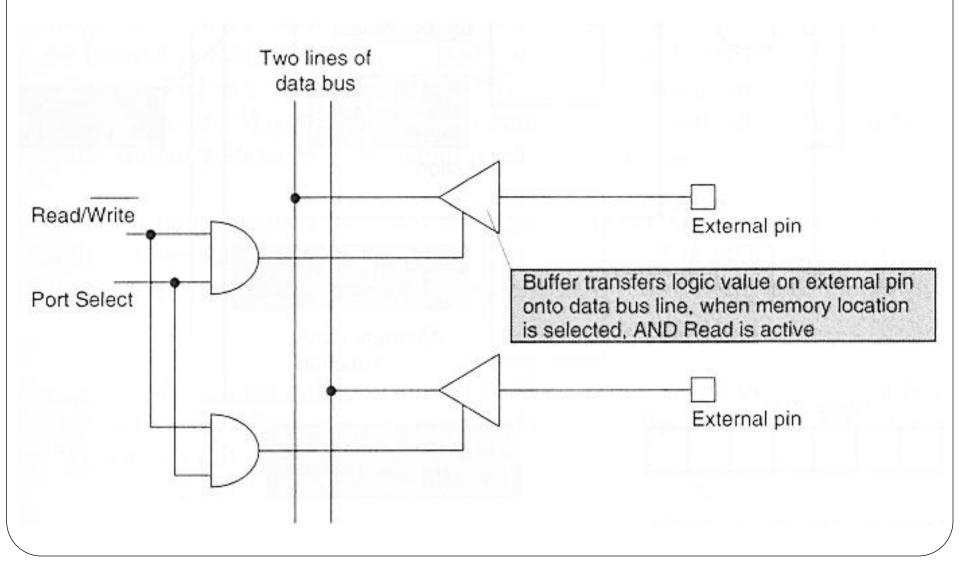

## Parallel I/O Input Structure

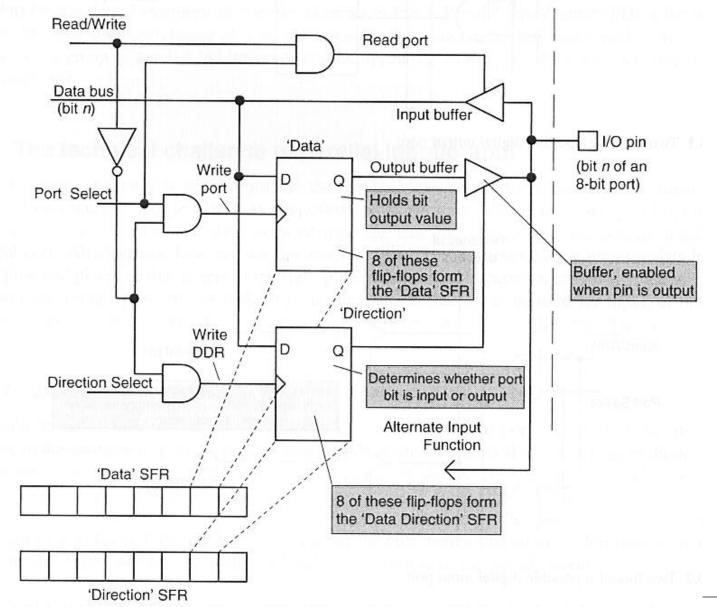

#### Parallel I/O Combined I/O Structure

#### Parallel I/O ports Main Features

- Simple memory mapped access

- Can be configured through software as either input or output

- Ability to set or reset individual bits

- Can have internal pull-ups

- Can drive small loads like LEDs

- Can be multifunction

- Different capability for pins (i.e. larger current)

## Parallel I/O ports

- For most ports, the I/O pin's direction (input or output) is controlled by the data direction register TRISx (x=A,B,C,D,E): a '1' in the TRIS bit corresponds to that pin being an input, while a '0' corresponds to that pin being an output

- The PORTx register is the latch for the data to be output. Reading PORTx register read the status of the pins, whereas writing to it will write to the port latch.

- Example: Initializing PORTB (PORTB is an 8-bit port. Each pin is individually configurable as an input or output).

- bcfSTATUS, RP0; select bank0bcfSTATUS, RP1clrfPORTBis clear PORTB output data latchesbsfSTATUS, RP0is select bank1movlw0xCFis value used to initialize data directionmovwfTRISBis PORTBis portB

- ; PORTB<3:0>=inputs

# Relationship between TRIS and PORT Registers

## Illustration: Displaying a Byte at an I/O Port (1 of 5)

- Problem statement:

- Write instructions to light up alternate LEDs at PORTC.

- Hardware:

- PORTC

- bidirectional (input or output) port; should be setup as output port for display

- Logic 1 will turn on an LED in Figure 2.10.

#### Illustration (2 of 5)

- Interfacing LEDs to PORTC

- Port C is F82H

- Note that PORT C is set to be an output!

- Hence, TRISC (address 94H) has to be set to 0

#### Illustration (3 of 5)

- Program (software)

- Logic 0 to TRISC sets up PORTC as an output port

- Byte 55H turns on alternate LEDs

- MOVLW 00 ;Load W register with 0

- MOVWF TRISC, 0

- MOVLW 0x55

- MOVWF PORTC,0

- ;Set up PORTC as output

- ;Byte 55H to turn on LEDS

- ;Turn on LEDs

- SLEEP ;Power down